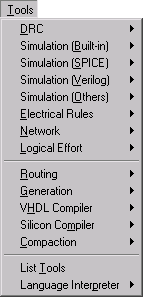

12-10: The Tools Menu |

12-10: The Tools Menu |

This menu is a collection of submenus that controls the different analysis and synthesis tools in Electric. For analysis, there are Design-Rule Checkers, a simulator, many simulation interfaces, and a network consistency checker. For synthesis, there are routers, PLA generators, a VHDL compiler, and a silicon compiler place-and-route system.

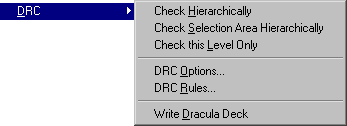

| This submenu controls the design-rule checkers. There is an incremental system which watches all design and displays warnings where appropriate. There are also two hierarchical checkers and an interface to the Dracula DRC system. |

| Check Hierarchically | This checks the current cell hierarchically (all geometry is checked, all the way down the hierarchy). | |

| Check Selection Area Hierarchically | This checks the current cell hierarchically, but only in the selected area. | |

| Check this Level Only | This command checks the current cell nonhierarchically (only geometry in the current cell is checked, not in any subcells). | |

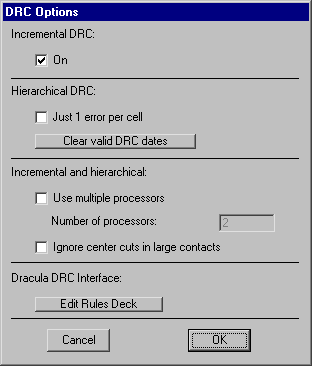

| DRC Options... |

This command lets you control a number of DRC options,

including whether or not the incremental DRC is running,

options for Dracula, and more.

|

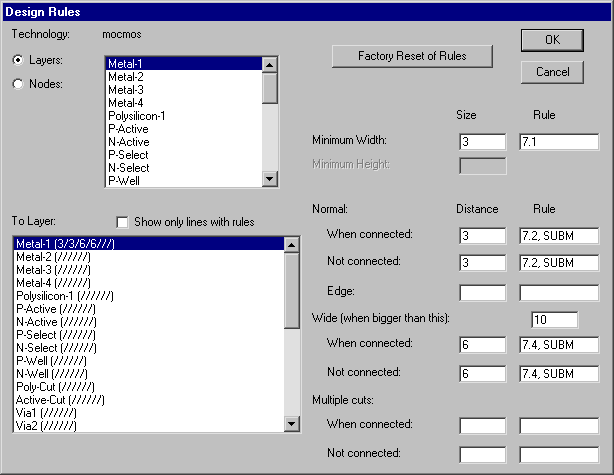

| DRC Rules... |

This command provides a way to examine and modify the design rules

(by using the "For layer" and "To layer" areas).

|

| Write Dracula Deck | This command tells the design-rule checker to produce an input deck for the Dracula design-rule checker. At the current time, only layout in the MOSIS CMOS (mocmos) technology can be checked in this manner. However, with the "Edit Dracula Deck" button of the DRC Options... dialog, rule sets may be defined for any technology. |

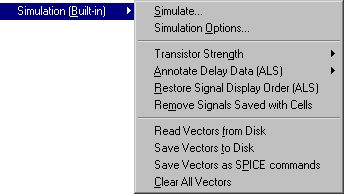

| This submenu controls the gate-level simulator in Electric. Electric comes with a simulator called ALS (Asynchronous Logic Simulator), but you can also add an IRSIM engine. In addition to controling live simulators, these commands can also be used to manipulate waveforms that come from batch simulators such as SPICE and Verilog. |

| Simulate... | This command causes the current cell to be simulated. For ALS simulation, the cell is converted to VHDL, the VHDL is compiled into a netlist, and the netlist is simulated. For IRSIM, a netlist is generated and the simulator is invoked. A waveform display is shown for viewing signal values. | ||

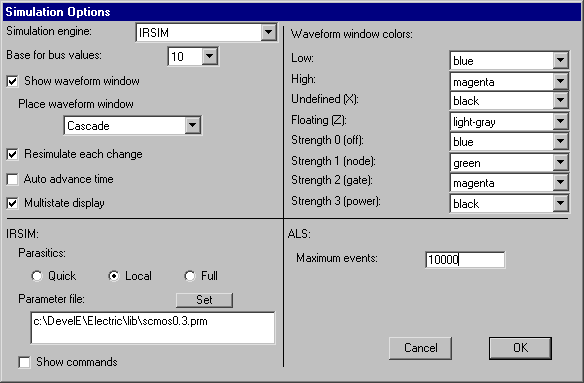

| Simulation Options... |

This command presents a dialog for control of simulation parameters.

The simulation engine can be selected (initially, Electric comes with only the ALS simulator,

but a built-in IRSIM engine is available from Static Free Software).

The "Resimulate each change"

item causes each change that is made to something being simulated to trigger resimulation and display of the results.

The "Auto advance time"

item tells the simulator to move the time cursor automatically when a new signal is added to the simulation.

The "Multistate display"

check tells the simulator to show signals in the layout or schematics window with texturing and color to indicate strength.

Without this, a simple on/off indication is drawn in the layout or schematics window.

The "Show waveform window"

check tells the simulator to create a separate window with waveform plots when simulation starts.

The waveform window can be cascaded (a separate overlapping window)

or tiled (placed in one half of the original circuit's window).

The radix of bus signals in the waveform window can be selected.

For ALS, the maximum number of events to simulate can be changed if you want to extend the simulator's range

(and memory usage).

For IRSIM, the level of parasitics and the file of parasitic information can be specified.

| |||

| Transistor Strength |

| |||

| Annotate Delay Data (ALS) |

| |||

| Restore Signal Display Order (ALS) | This command restores the default set of signals in the waveform display, which is useful if they have been rearranged or if some signals were deleted. It only works for the ALS simulator. | |||

| Remove Signals Saved with Cells | The waveform display remembers the signal names that are associated with each cell. When the user rearranges signals, it is preserved for the next time that cell is simulated. This command clears the saved list of signal names associated with every cell so that the waveform window will use a default set. | |||

| Read Vectors from Disk | This command causes a file of test vectors to be read from disk. You will be prompted for the file name. | |||

| Save Vectors to Disk | This command causes the current set of test vectors to be saved to disk. You will be prompted for the file name. | |||

| Save Vectors as SPICE commands | This command exports the current set of test vectors as a SPICE deck. | |||

| Clear All Vectors | This command erases all test vectors from the simulation. |

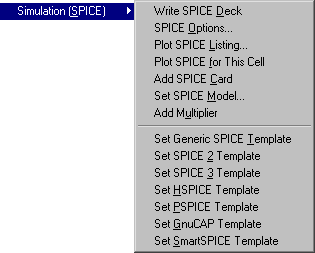

| This submenu controls the SPICE simulator, including deck generation and plotting SPICE output. |

| Write SPICE Deck | This command generates an input deck for the SPICE circuit-level simulator. Because SPICE is not an interactive system, it is necessary to specify inputs and outputs in the circuit. This is done by placing Source and Meter components (from the New Analog Component submenu of the Edit menu), parametrizing them with the actual SPICE message, and connecting them to the circuitry. It is also necessary to specify Transient or DC analysis by placing an appropriate Source component in the cell. |

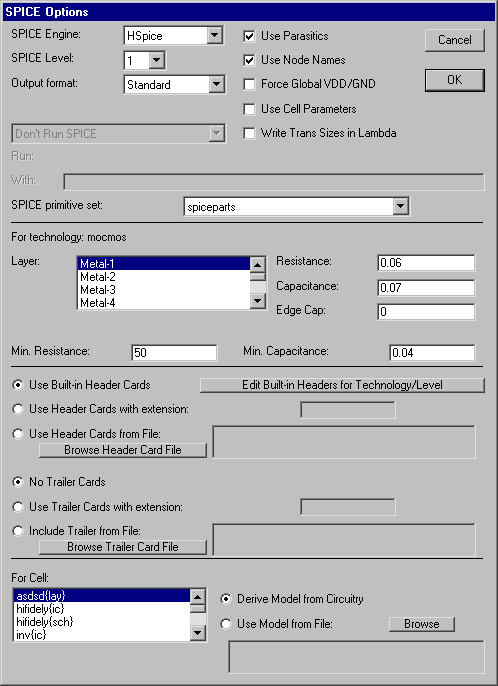

| SPICE Options... |

This command allows many SPICE options to be controlled, for example,

the SPICE format (SPICE 2, SPICE 3, HSPICE, PSPICE, GnuCAP, or SmartSPICE);

control of parasitics in the deck;

control of SPICE execution (UNIX systems only);

control of header, trailer, and individual cell model cards;

and much more.

| |

| Plot SPICE Listing... | This command reads the output of a SPICE run and shows the signals in a waveform window. You will be prompted for the name of the SPICE output file. | |

| Plot SPICE for This Cell | This command reads the output of a SPICE run and shows the signals in a waveform window. This command presumes that the SPICE output file has the same name as the current cell (with appropriate extensions). For example, if you are editing cell "myclock{lay}", this command will look for file "myclock.spo". | |

| Add SPICE Card | This command allows you to click in the design and type a SPICE card that will be inserted into the generated deck. | |

| Set SPICE Model... | This command allows you to change the SPICE model of the currently selected node. | |

| Add Multiplier | This command places a multiplier factor on the currently selected node. This factor is used to scale the transistor sizes. | |

| Set Generic SPICE Template | This command allows you to create a SPICE template for the current cell. | |

| Set SPICE 2 Template | This command allows you to create a template specifically for SPICE 2. | |

| Set SPICE 3 Template | This command allows you to create a template specifically for SPICE 3. | |

| Set HSPICE Template | This command allows you to create a template specifically for HSPICE. | |

| Set PSPICE Template | This command allows you to create a template specifically for PSPICE. | |

| Set GnuCAP Template | This command allows you to create a template specifically for GnuCAP. | |

| Set SmartSPICE Template | This command allows you to create a template specifically for SmartSPICE. |

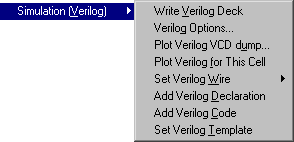

| This submenu controls the generation of Verilog simulation netlists. |

| Write Verilog Deck | This command generates an input deck for the Verilog simulator. |

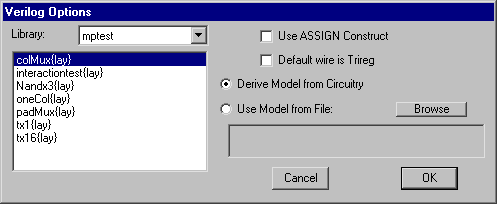

| Verilog Options... |

This command generates displays a dialog for controlling Verilog deck generation.

| |

| Plot Verilog VCD Dump | This command reads a dump file (the output of Verilog simulation) and displays the result in a waveform window. | |

| Plot Verilog for This Cell | This command reads the output of a Verilog run and shows the signals in a waveform window. It presumes that the Verilog output file has the same name as the current cell (with appropriate extensions). For example, if you are editing cell "myclock{lay}", this command will look for file "myclock.dump". | |

| Set Verilog Wire | This command lets you set the type of Verilog wire that the current arc will produce (either Wire, Trireg, or Default). The Default option uses the setting from the Verilog Options... dialog. | |

| Add Verilog Declaration | This command allows you to click in the design and type Verilog declarations that will be inserted into the generated deck. | |

| Add Verilog Code | This command allows you to click in the design and type Verilog code that will be inserted into the generated deck. | |

| Set Verilog Template | This command allows you to create a Verilog template when defining new primitives. |

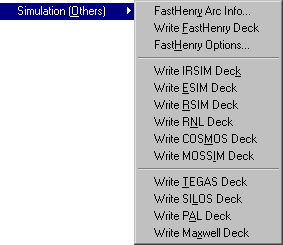

| This submenu allows input decks to be written for many different simulators. |

| FastHenry Arc Info... |

| ||

| Write FastHenry Deck... | This command generates a FastHenry deck from the current cell. | |||

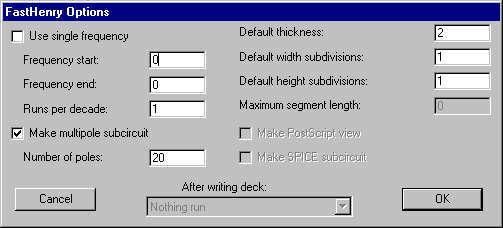

| FastHenry Options... |

This command presents a dialog of options for FastHenry deck generation.

The frequency and multipole options control flags that are placed in the deck.

The default thickness and subdivision fields provide values that are used when no overrides are specified for individual arcs.

| |||

| Write IRSIM Deck | This command generates an input deck for the IRSIM switch-level simulator. | |||

| Write ESIM Deck | This command generates an input deck for the ESIM switch-level simulator (nMOS only, no timing). | |||

| Write RSIM Deck | This command generates an input deck for the RSIM switch-level simulator (nMOS only). | |||

| Write RNL Deck | This command generates an input deck for the RNL switch-level simulator (nMOS only, Lisp-like interface). | |||

| Write COSMOS Deck | This command generates an input deck for the COSMOS switch-level simulator (MOS only). | |||

| Write MOSSIM Deck | This command generates an input deck for the MOSSIM switch-level simulator (MOS only). | |||

| Write TEGAS Deck | This command generates an input deck for the TEGAS/TEXSIM gate-level simulator. | |||

| Write SILOS Deck | This command generates an input deck for the SILOS simulator. | |||

| Write PAL Deck | This command generates an input deck for the Abel PAL generator/simulator. | |||

| Write Maxwell Deck | This command generates an input deck for the Maxwell simulator. |

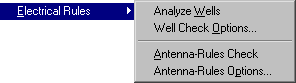

| These commands do static analysis of the circuit, which include well analysis and antenna rules. |

| Analyze Wells | This command examines the current cell and checks all well areas for proper electrical rules. The farthest distance from a well contact to the edge of its implant is shown. |

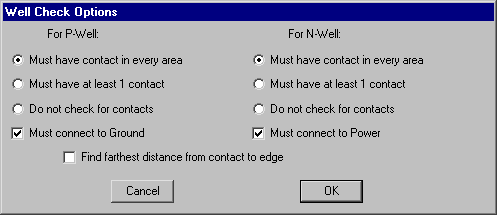

| Well Check Options... |

This presents a dialog with Well and Substrate Checking options.

You can choose to require one contact per area,

or only one contact anywhere on the chip.

You can also check for proper power and ground connections.

| |

| Antenna-Rules Check | This command examines the current cell and all below it for antenna rules violations. Antenna rules ensure that there is no path from a large area of metal or poly to a small number of transistor gates. |

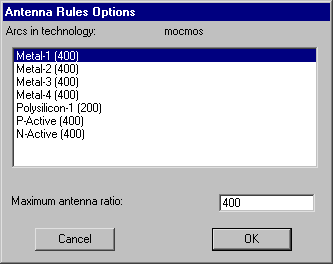

| Antenna-Rules Options... |

This presents a dialog with Antenna rule ratio limits.

|

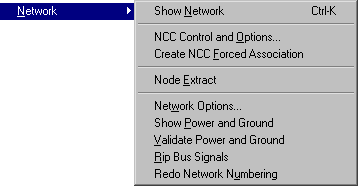

| This submenu controls miscellaneous network functions, including a Network Consistency Checking (NCC) facility. Some systems call network consistency checking "LVS" (Layout vs. Schematic), but Electric uses the term NCC because it can compare any two cells, not just layout vs. schematic. |

| Show Network | This command shows the equivalent to the currently highlighted network in all other windows. It also works for network names seleted in a text window. If this cell has been run through the network consistency checker, that information will be used. | ||

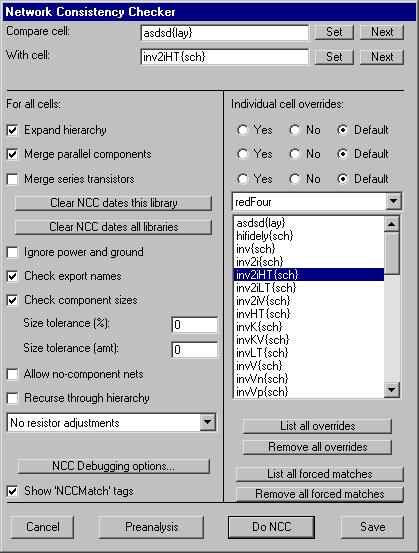

| NCC Control and Options... |

This presents a dialog for controlling the network consistency checker.

On top are the two cells whose networks are to be compared.

If there are two cells currently being displayed, they are loaded into these fields.

The lower portion controls the NCC process. On the left are the NCC controls, and on the right half are per-cell overrides of some of these settings. The bottom has buttons for running NCC or Preanalysis. | |||

| Create NCC Forced Association | This command places an NCC-match tag on the currently select object. By changing the name, and setting the same name on objects in different cells, those objects are forced to match during NCC. | |||

| Node Extract [7-3] | This command extracts connectivity from a cell that has only geometry (pure-layer nodes). Such cells are the result of reading external format files, such as CIF and GDS. The pure-layer nodes are removed and replaced with a connected network of nodes and arcs. Unfortunately, the node extractor is only partially implemented and should not be counted-on to properly extract. Also, it does not recognize transistors. | |||

| Network Options... |

| |||

| Show Power and Ground | This command highlights all of the power and ground networks in the current cell. | |||

| Validate Power and Ground | This command checks all power and ground networks in the circuit to be sure that they are named sensibly. | |||

| Rip Bus Signals [7-6] | This command takes the currently selected bus wire and adds wire taps for each signal on the bus. The wires run perpendicular to the bus and are labeled with their signal. | |||

| Redo Network Numbering [6-12] | This command is not generally needed but may be useful if you suspect that the network information is incorrect. |

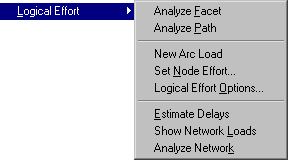

| This command does Logical Effort analysis, which determines the transistor ratios to use in digital schematic components in order to get optimal circuit speed. |

| Analyze Cell | This command examines the current cell and annotates all schematic gates with fanout information. | ||

| Analyze Path | This command examines the circuitry between the two highlighted components and annotates the gates with fanout information. | |||

| New Arc Load | This command creates a special "load" symbol that has capacitance and can connect to the circuit to declare a load there. The capacitance value can be changed by double-clicking and typing a new value. | |||

| Set Node Effort... | This command allows you to set an overriding logical effort value on the currently selected node. This value can be changed by double-clicking and typing a new value. | |||

| Logical Effort Options... |

This command provides options for controlling the Logical Effort tool.

| |||

| Estimate Delays | This command examines each network in the circuit and calculates load factors. It is not generally useful, and applies to Logical Effort calculations. | |||

| Show Network Loads | This command lists every network in the current cell, showing the wire length, load, and other information. | |||

| Analyze Network | This command shows a detailed analysis of the currently selected network, including the area and perimeter information for each layer, as well as load information. |

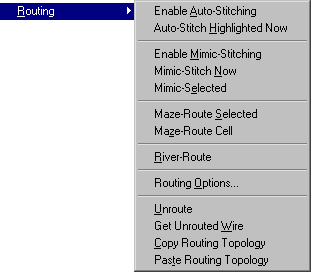

| This submenu controls a number of wire routing facilities. |

| Enable Auto-Stitching | This command instructs the router to watch all subsequent layout activity and to place arcs wherever touching nodes create implicit connections. It is useful to issue this command before generating arrays, because the array may produce many implicit connections that this router will make explicit. The menu entry changes to Stop Auto-Stitching to disable the function. | ||

| Auto-Stitch Highlighted Now | This does auto-stitching only in the currently highlighted area. The highlighted area is defined as the bounding rectangle of everything that is highlighted. A more precise way of defining a highlighted area is to use the rectangle select button to drag a rectangle on the screen. | |||

| Enable Mimic-Stitching | This command instructs the router to watch all subsequent layout activity and to automatically create other arcs in similar locations whenever you create one by hand. The menu entry changes to Disable Mimic-Stitching to disable this function. | |||

| Mimic-Stitching Now | This command instructs the router to mimic the last arc that was created. It is not necessary for the Mimic Stitcher to be enabled. | |||

| Mimic-Selected | This command instructs the router to mimic the selected arc. It is not necessary for the Mimic Stitcher to be enabled. | |||

| Maze-Route Selected | This command runs the maze router in the selected area. All occurrences of the Unrouted wire will be replaced with real geometry. | |||

| Maze-Route Cell | This command runs the maze router in the current cell. All occurrences of the Unrouted wire will be replaced with real geometry. | |||

| River-Route | This command runs the river-router in the current cell. All occurrences of the Unrouted wire will be replaced with real geometry. | |||

| Routing Options... |

This command provides a dialog for control of the stitching routers.

| |||

| Unroute | This command takes the currently selected network(s) and converts them to unrouted wires. After this command, you can maze-route or river-route the unrouted wires. | |||

| Get Unrouted Wire | The Unrouted wire of the Generic technology is used to define routing requirements (see Section 7-9). This command selects the Generic arc so that subsequent wiring commands will use it. This is necessary in order to do maze and river-routing. | |||

| Copy Routing Topology | This command remembers the network of connections in the current cell for subsequent creation in another cell (specified with Paste Routing Topology). | |||

| Paste Routing Topology | This command examines the current cell and compares its network to the one that was copied (with Copy Routing Topology). Where there are missing connections in this cell, the command creates Unrouted arcs to connect them. |

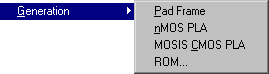

| This command provides a pad frame generator and two PLA generators. All will run faster if the design-rule checker is turned off first. |

| Pad Frame [9-8] | This command prompts for a disk file that describes the placement of pads around a core cell. The file includes information about the library that contains the pads and also the connection between the pads and ports on the core cell. | ||

| nMOS PLA [9-7] | This command prompts for a personality table and generates nMOS layout, complete with power and clocking. See the description of the PLA generator for a sample personality table. | ||

| MOSIS CMOS PLA [9-7] | This command prompts for two personality tables: the AND and the OR tables. It also offers options about the location of inputs and outputs. See the description of the PLA generator for a sample CMOS personality table. | |||

| ROM... [9-7] |

|

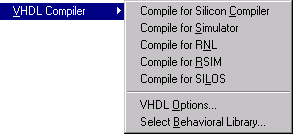

| This submenu provides direct control of the VHDL compiler, which translates VHDL textual descriptions into netlists. Besides controlling which format netlist is generated, it is also possible to determine whether the netlist of the VHDL is to be stored in memory (in a cell) or on disk. |

| Compile for Silicon Compiler | This command causes the VHDL in the current cell to be compiled into a netlist for the silicon compiler. If the current cell is not a VHDL view, the VHDL view is used. If VHDL disk files are being used instead of cells, the file "XXX.vhdl" is read, where XXX is the cell name of the current cell. If netlists are being written to disk, the file "XXX.sci" is written. | ||

| Compile for Simulation | This command causes the VHDL in the current cell to be compiled into a netlist for simulation. If the current cell is not a VHDL view, the VHDL view is used. If VHDL disk files are being used instead of cells, the file "XXX.vhdl" is read, where XXX is the cell name of the current cell. If netlists are being written to disk, the file "XXX.net" is written. | |||

| Compile for RNL | This command causes the VHDL in the current cell to be compiled into a RNL simulator netlist. If the current cell is not a VHDL view, the VHDL view is used. If VHDL disk files are being used instead of cells, the file "XXX.vhdl" is read, where XXX is the cell name of the current cell. If netlists are being written to disk, the file "XXX.net" is written. | |||

| Compile for RSIM | This command causes the VHDL in the current cell to be compiled into a RSIM simulator netlist. If the current cell is not a VHDL view, the VHDL view is used. If VHDL disk files are being used instead of cells, the file "XXX.vhdl" is read, where XXX is the cell name of the current cell. If netlists are being written to disk, the file "XXX.net" is written. | |||

| Compile for SILOS | This command causes the VHDL in the current cell to be compiled into a SILOS simulator netlist. If the current cell is not a VHDL view, the VHDL view is used. If VHDL disk files are being used instead of cells, the file "XXX.vhdl" is read, where XXX is the cell name of the current cell. If netlists are being written to disk, the file "XXX.sil" is written. | |||

| VHDL Options... |

| |||

| Select Behavioral Library... | When compiling for simulation, behavioral models will be included if they are found in the current library. This command allows an alternate library to be searched for the models. Note that each model can be found in the "netlist-als-format" view of an appropriately named cell. |

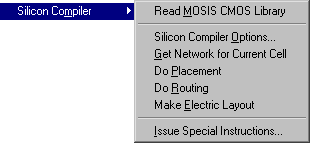

| This submenu is an extensive system for placing and routing standard cell libraries from a structural VHDL description. Simply run each command in sequence: select a library, set options, obtain a netlist, place, route, and make Electric layout. |

| Read MOSIS CMOS Library | This command requests that the MOSIS CMOS standard cell library be used. This cell library is not guaranteed to be correct and exists only for illustration purposes. See the "Silicon Compiler" section of Chapter 9 for a description of the cells in this library. |

| Silicon Compiler Options... | This command presents a dialog that allows the setting of various parameters for the silicon compilation process. | |

| Get Network for Current Cell | This command gets a netlist for the current cell. If the current cell is not a netlist, and the netlist associated with this cell is missing or out of date, the VHDL Compiler will be used to create a netlist. If the current cell is not VHDL, and the VHDL associated with this cell is missing or out of date, the VHDL will be generated from a schematic. | |

| Do Placement | This command computes the placement of standard cells. | |

| Do Routing | This command computes the routing among the placed standard cells. | |

| Make Electric Layout | This command generates final circuitry from the computed placement and routing. The design-rule checker is turned off during this step. | |

| Issue Special Instructions... | This command allows you to communicate directly with the Silicon Compiler. Only those familiar with the system should do this (the other commands in this submenu handle standard functions without the need to know how the compiler works). |

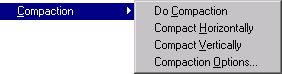

| This submenu controls the layout compactor. |

| Do Compaction | This command compacts the layout in the current window to design-rule distances, using single-axis compaction. It alternates horizontal and vertical compaction until no additional space can be saved. Compaction is done downward and to the left. | ||

| Compact Horizontally | This command instructs the compactor to compact the current cell one time in the horizontal direction. | |||

| Compact Vertically | This command instructs the compactor to compact the current cell one time in the vertical direction. | |||

| Compaction Options... |

|

This command lists all of the tools, showing which ones are active.

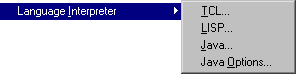

| There are language interpreters in Electric: TCL, LISP, and Java. The interpreters can be activated with the subcommands here. Once activated, you communicate with them in the messages window. Note that, because of copyright restrictions, the LISP interpreter is not part of the standard GNU distribution and must be obtained separately from Static Free Software. The TCL and Java interpreters must also be obtained separately. See the installation instructions for UNIX, Section 1-3, Macintosh, Section 1-4, and Windows, Section 1-5. |

| Previous | Table of Contents | Next |