9-10: VHDL Compiler |

9-10: VHDL Compiler |

Use the Compile for Silicon Compiler, Compile for Simulation, Compile for RNL, Compile for RSIM, and Compile for SILOS subcommands of the VHDL Compiler command of the Tools menu to generate appropriate format netlists.

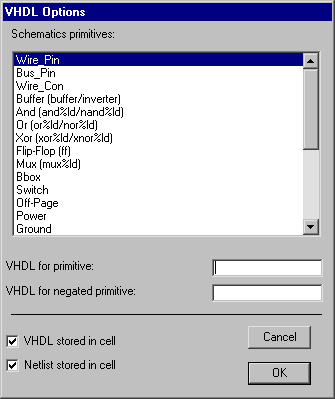

| By default, the compiler reads VHDL from the "vhdl" view of the cell in the current window and writes netlists to appropriate "netlist" views of this cell. This can be changed with the VHDL Options... subcommand of the VHDL Compiler command of the Tools menu. By unchecking "VHDL stored in cell", the VHDL is taken from the file "XXX.vhdl", where XXX is the current cell name. By unchecking "Netlist stored in cell", the netlist is written to the file "XXX.sci" (for the silicon compiler), "XXX.net" (for the simulator, RNL, and RSIM), or "XXX.sil" (for SILOS) where XXX is the current cell name. Recheck these items to locate the text in the cells. |  |

The Options dialog also controls how the VHDL generator produces symbol names for schematics nodes. The dialog shows each schematics node, along with its regular and negated VHDL symbol (the use of "%d" is replaced by the number of inputs on the gate).

Another feature of the VHDL compiler is its ability to generate VHDL from a schematic or layout. Use the Make VHDL View command of the View menu to convert the current cell into VHDL. Note that the state of the "VHDL stored in cell" entry of the Options dialog determines whether this VHDL is written to disk or a cell.

| Previous | Table of Contents | Next |