10-3: VHDL Interface (ALS) |

10-3: VHDL Interface (ALS) |

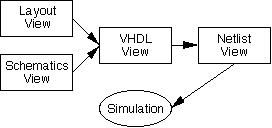

| The user should be aware that the ALS simulator translates the circuit into VHDL, then compiles the VHDL into a netlist for simulation. This means that when a layout or schematic is simulated, two new views of that cell are created: "VHDL" and "netlist-als-format". Use the Edit VHDL View of the View menu to see the VHDL code. |  |

Because cells are kept in memory, it is possible that the size of the VHDL (or more likely the size of the netlist) will be too large. Electric can be instructed to keep either document on disk rather than in a cell, which saves memory. Use the VHDL Options... subcommand of the VHDL Compiler command of the Tools menu and uncheck the "VHDL stored in cell" or "Netlist stored in cell" items to place either or both on disk. See Section 9-10 for more information on the VHDL Compiler.

When simulation is requested, the cell in the current window is simulated. Date checking is performed to determine whether VHDL translation or netlist compilation is necessary. If you are currently editing a VHDL cell, it will not be regenerated from layout, even if the layout is more recent. Similarly, if you are currently editing a netlist cell, it will not be regenerated from VHDL, even if that VHDL is more recent. Thus, simulation of the currently edited cell is guaranteed.

Note that the presence of VHDL in the path to simulation means that it can simulate VHDL that is entered manually. You can type this VHDL directly into the cell, or it can be read from disk using the Read Text Cell... command of the Cells menu. Also, you can explicitly request that VHDL be produced from schematics or layout with the Make VHDL View command of the View menu.

This complete VHDL capability, combined with the Silicon Compiler which places and routes from VHDL descriptions, gives Electric a powerful facility for creating, testing, and constructing complex circuits from high-level specifications. See Section 9-9 for more on the Silicon Compiler.

| Previous | Table of Contents | Next |