9-7-5: Graphical User Interface (GUI)

Chapter 9: Tools

| 9-7: Network Consistency Checking (NCC) 9-7-5: Graphical User Interface (GUI) |

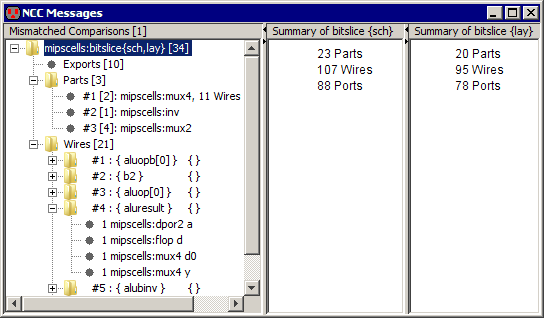

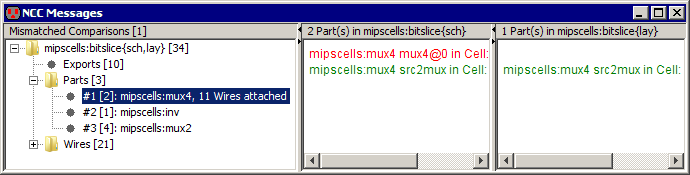

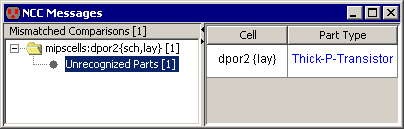

When NCC finds mismatches, a window pops up displaying the mismatches. Below is a typical display with some essential features.

The left side of the window is a tree providing an overview of the kinds of mismatches that NCC found. The right side has information corresponding to the currently selected tree node(s).

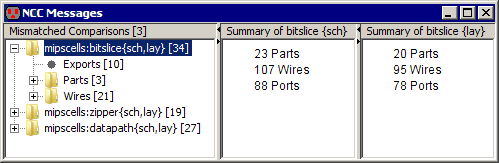

Each top-level tree node corresponds to a comparison of two cells. In the above example, the label on the top-level node indicates that the comparison that failed was between the cells: "bitslice{sch}" and "bitslice{lay}" in the library: "mipscells". If the two cells have different names or are from different libraries, then their names are shown individually. For example, "libraryA:gateA{sch} & libraryB:gateB{sch}". The number in square brackets at the right end of the cell names, in this example "[34]", is the number of mismatches.

In general, if you see a tree node with a number in square brackets, then this number is the total number of mismatches grouped under this node.

Selecting a top-level tree node displays the number of parts, wires, and ports in the compared cells in the right part of the window. For all other nodes, the right side of the window displays a list of component names arranged in different ways, as described in subsequent sections. Some components are highlightable, in which case their names are printed as blue, red, or green hyperlinks.

A top-level node has one or more subnodes. Subnodes can have the following types: Exports, Parts, Wires, Parts (hash code), Wires (hash code), Sizes, Export Assertions, Export/Global Network Conflicts, Export/Global Characteristics Conflicts, and Unrecognized Parts.

For more information on the NCC graphical user interface, see:

Kao, Russell, Ivan Minevskiy, and Jon Lexau, "Design Notes for Electric's Network Consistency Check",

Sun Microsystems Laboratories Technical Report 2006-152, January 2006.

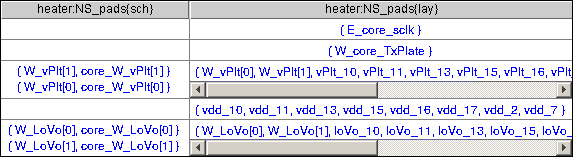

The exports node is always a leaf node with the name "Exports [X]", where "X" is the number of export mismatches in this comparison. Selecting an exports node displays a table on the right side of the NCC graphical window (see below). The table has two columns - one per compared cell. The header contains cell names. Each row corresponds to a mismatch. A table cell has zero or more export lists. An export list is a list of all the exports found on a network and is displayed as a list of export names surrounded by curly brackets "{ }". Each export list is a single hyperlink which highlights all the exports in the list.

Multiple export lists in a table cell occur when a single network in one design (e.g. the schematic) has one or more exports that match multiple exports attached to more than one network in the other design (e.g. the layout). For example, the mismatch on the third row from the top in the figure below has layout exports (the second column) attached to a single network matching schematic exports (the first column) attached to two networks.

An empty table cell means one design has exports that match no exports with the same names in the other design. For example, the mismatch in the top row above has the layout export "E_core_sclk" matching no exports in the schematic.

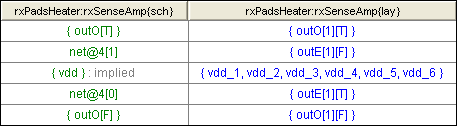

Some exports are implied. For example, if a schematic cell uses a global ground, but does not contain an export for that ground, then NCC will automatically insert an implied export for ground. This is done because most often the corresponding layout cell has a ground export, and we want the schematic and layout cells to match. Implied exports are not hyperlinked and have ": implied" added to their names (see below).

When NCC does not find any topological mismatches, it attempts to suggest possible matches for exports that failed to match by name. Such suggestions are printed in green. The first row of the table below indicates that the "outO[1][T]" export in the layout topologically matches the "outO[T]" export in the schematic, even though they have different names. The second row indicates that the "outE[1][F]" export in the layout topologically matches the "net@4[1]" wire in the schematic, even though the "net@4[1]" wire has no exports. Note that a wire name is not an export list and is not surrounded by curly brackets.

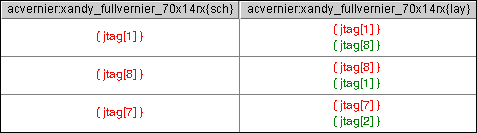

Exports that match by name, but are not on equivalent networks, have red hyperlinks. Such exports might have suggested matches as well, which are printed in green. In the first row of the table below, the "jtag[1]" export in the schematic does not topologically match the "jtag[1]" export in the layout, but does match the "jtag[8]" export in the layout.

NCC finds mismatches by applying two partitioning techniques in sequence. First it uses local partitioning and then it uses hash code partitioning. If local partitioning finds mismatches, then NCC reports only those. The mismatches in local partitioning of parts and wires are grouped under nodes with names "Parts [X]" and "Wires [X]", where "X" is the number of mismatched local partitioning classes (see figure below). Each class node represents a class of parts or wires sharing the same local characteristics.

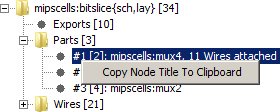

Parts are partitioned into equivalence classes based upon their type and the number of wires attached to them. The figure below shows a list of two part classes.

The tree node corresponding to the

first class is selected and has the name

#3 [4]: mipscells:mux2

which has the following meaning:

#3 The sequence number of this class[4] The number of mismatched parts in one of the two cells, whichever is

bigger. In our example, the schematic cell has 4 mismatched part

in this class and the layout has 3 mismatched parts in this

class. The maximum of 4 and 3 is 4 and, therefore, the tree node

has "[4]" in its name.mipscells Part librarymux2 Part

typeIn the example above, part types were enough to partition parts into classes. In many other cases, like the one in the figure below, types are not enough and the number of different wires attached to a part is employed as an additional partitioning criterion.

When a part class node is selected, the right half of the window displays a two-column table. Each column corresponds to one of the compared cells and has a list of that cell's parts which belong to the selected part class. Matched parts are printed in green.

Parts on the same line match each other. Mismatched parts are printed in red in no particular order.

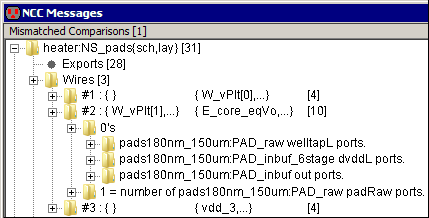

NCC partitions wires into equivalence classes based upon the number of different port types attached to them. Examples of port types include an NMOS "gate" port, a PMOS "diffusion" port, and a NAND "output" port. Port type counts are represented as a list of leaf nodes under the wire class node. Since zero-value counts at the beginning of the list tend to be numerous and are rarely used by designers, they are further grouped under a "0's"; node.

For example, in the figure below, the second wire class is expanded and we can see its four characteristics, the first three of which are "zero". The first characteristic has a leaf node called "pads180nm_150um:PAD_raw welltapL ports", which means that wires in this class are not attached to the port "welltapL" of the part "PAD_raw" from the library "pads180nm_150um".

The fourth characteristic is "1 = number of pads180nm_150um:PAD_raw padRaw ports". The name suggests that all wires in this class are connected to the "padRaw" ports of 3 instances of parts with type "PAD_raw" from library "pads180nm_150um".

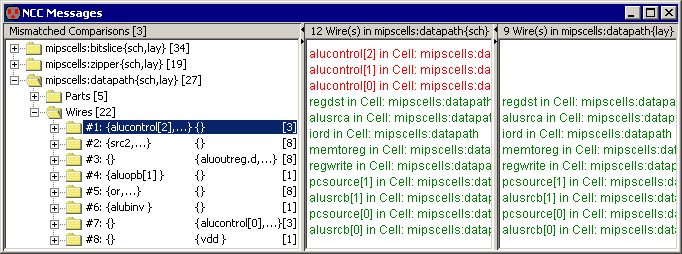

When a wire class node is selected, the right half of the window displays a two-column table (see figure below). Each column corresponds to one of the compared cells and has a list of that cell's wires which belong to the selected wire class. Matched wires are printed in green, the two wires on the same line match each other. Mismatched wires are printed in red in no particular order.

The tree node names contain the first mismatched wires from both lists.

For example, in the above figure, the first wire class has the node name

#1 : {alucontrol[2],...} { } [3]

which has the following meaning:

#1 The sequence number of this class.{alucontrol[2],...} The first mismatched wire in the first cell's list is called "alucontrol[2]"

The ellipsis after the name suggest that there is more than one wire in the list.{ } The name of the mismatched wire in the second cell's list (nothing is found).[3] The number of mismatched wires in one of the two cells, whichever is

bigger. In our example, the schematic cell has 3 mismatched wires

in this class, and the layout has 0 mismatched wires in this

class. The maximum of 3 and 0 is 3, and therefore, the tree node

has "[3]" in its name.If local partitioning fails to find a mismatch, then NCC reports mismatches found by hash code partitioning under the nodes labeled "Parts (hash code)" and "Wires (hash code)". Unlike their local partitioning counterparts, hash code partitioning classes do not have any characteristics.

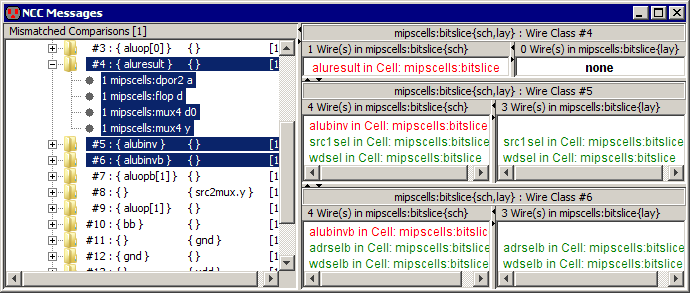

It is possible to select more than one class by holding the Control (Command on Macintosh) or the Shift key during selection. In this case, the right side will have multiple rows, one row per class. The figure below shows what is displayed when the three wire classes in the figure above are selected. Up to five classes can be displayed at once. Rows are arranged in the order in which the classes are selected.

Selecting one or more subnodes of a class node is equivalent to selecting the class node itself. This means that no class appears twice in the table on the right. If some node of a type different from Parts, Wires, Parts (hash code), or Wires (hash code) is selected as well, then it has a higher display priority and its contents are displayed instead. For example, if an exports node was selected with the three wire class nodes, then the export table would be displayed on the right.

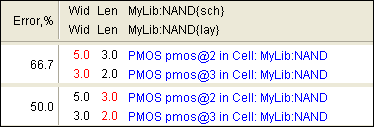

Both length and width mismatches in transistor, resistor, and other component sizes are collected under "Sizes [X]" node, where "X" is the total number of size mismatches. The mismatch is reported as both the percent and the ratio difference. Resistor size mismatches are reported here, because polysilicon resistors in both schematics and layout have lengths and widths.

On the right side of the window, mismatches are arranged into a table sorted in the descending order of the relative error (see example above). Each mismatch occupies one row and has four columns. The first column contains the relative error of the mismatch. The second and third columns have widths and lengths of the corresponding parts in two cells. The mismatched value is printed in red. The last column has hyperlinked part names.

If a transistor has both a length and a width mismatch, then these mismatches are displayed in separate rows (e.g. the first and the second rows above).

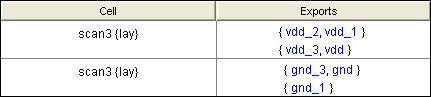

It is very common for a layout cell, A,

to have multiple ground wires that are connected by it's

parent cell, B. For example,

cell A may have a wire with the

export "gnd" and a different wire

with the export "gnd_1". When

cell B instantiates A,

cell B connects A's

exports "gnd" and "gnd_1".

However, A's schematic

typically has only one combined "gnd"

wire. When NCC compares A's

schematic and layout, it finds that the ground wires mismatch. As a

solution, the designer adds the following NCC annotation into A's

layout cell:

exportsConnectedByParent gnd gnd_1

This annotation constitutes a promise

that whenever A is

instantiated, its exports "gnd"

and "gnd_1" will be connected.

Then, when NCC compares A's schematic and layout, it assumes that the

promise has been kept and the comparison passes. However, when NCC

compares B's schematic and

layout, it checks to see if the designer is keeping the promise. If

the promise is not kept, and no new promise to connect exports in the

next parent is given, then NCC reports an export assertion error in

the "Export Assertions" leaf node.

When an "Export Assertions" node is selected, it displays a table with two columns and one or more rows (see below). Each row corresponds to a broken promise. The first column has cell names. The second column lists exports that the designer promised would be connected, but which remained disconnected. The exports are organized into two or more export lists. Each export list is a comma-separated list of exports enclosed in curly brackets "{ }". Exports in the same list are connected. Exports in different lists are disconnected. The designer promised that all exports in all lists would be connected.

All exports are individually highlightable. For example, if the designer clicks on the "vdd_1" export then NCC will open up a window for cell "scan3{lay}" and highlight the net connected to the export "vdd_1".

Tip: If it the design includes multiple instances of cell "rectifier{lay}" then the designer can find out which particular instance failed to keep the promise by typing control-U which will pop up a level in the hierarchy.

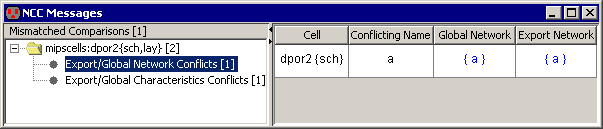

In an export/global network conflict, a cell has both an export and a global signal with the same name, but their networks are topologically different (see below). Both the global network export and the cell export are highlightable.

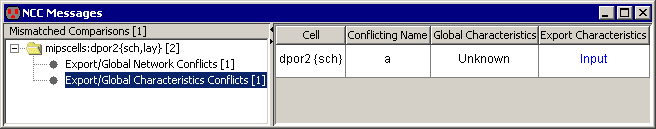

In an export/global characteristics conflict, one cell also has both an export and a global signal with the same name, but their characteristics differ (see below). The cell export can be highlighted by clicking on its characteristics.

This node has a list of parts (transistors and resistors) with unrecognized types (see below). Each part can be highlighted by clicking on its type.

The total number of mismatched cell comparisons is displayed in square brackets on the top of the tree. Only comparisons that did not pass NCC tests are counted and displayed. Each failed comparison corresponds to one top-level tree node. By default, NCC halts after the first failed comparison and, therefore, the tree contains just one failed comparison. If the user configures the NCC Preferences to continue even after finding mismatched cells, then NCC compares all cells and displays all that mismatch. When multiple cells have mismatches, the left pane will display more than one top-level node as shown below.

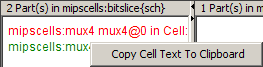

Right-clicking on a tree node or a table cell pops up a menu with an option to copy the node name or the cell text to the system clipboard (see below).

|

|

| Previous | Table of Contents | Next |