9-10-1: Parasitic Extraction

Chapter 9: Tools

| 9-10: Extraction 9-10-1: Parasitic Extraction |

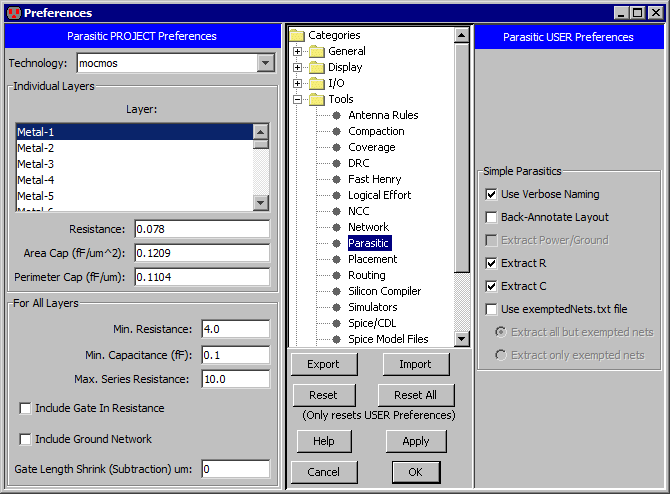

Parasitic Extraction is used by netlisters and other parts of the system that need to know about geometric factors. Control of parasitic extraction is done with the Parasitic Preferences (in menu File / Preferences..., "Tools" section, "Parasitic" tab).

The left side of the dialog has Project Preferences. Each layer of every technology is listed, and you can set its unit resistance, area capacitance, and edge capacitance. The bottom section controls values for every layer in a technology. You can set the minimum resistance and capacitance, as well as the maximum series resistance. The maximum series resistance breaks long single PI models into series of distributed PI models. "Include Gate In Resistance" requests that a transistor's gate area be included in overall area calculations for resistance determination. "Include Ground Network" requests that ground networks be analyzed. The "Gate Length Shrink" is a compensation factor for gate lengths. Some process technologies shrink the gate length by a fixed amount.

The right side of the dialog has User Preferences.

Exempted Nets file format. One line per network. A network is specified by a library name, cell name, and net name. When nets are not extracted, a lumped capacitance value may be specified to use on the network. This last argument is optional (0 if not specified) and ignored when the exempted nets are the only nets extracted.

libraryName cellName netName [replacementCapValue]

Example:

myLib myCell{lay} net@0

myLib myCell{lay} in_a

| Previous | Table of Contents | Next |